Datasheet

# High-speed 3.3 V / 5 V RS485 transceiver with ±12 kV IEC 61000-4-2 contact ESD protection

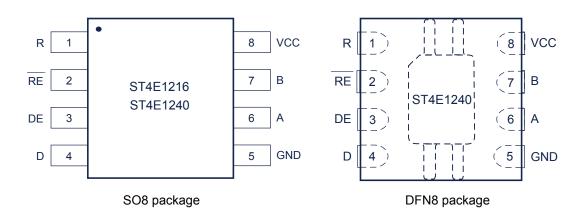

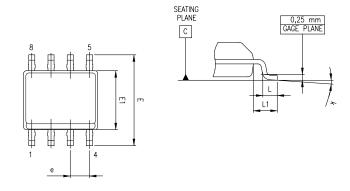

SO8 (4.90 x 3.91 mm)

DFN8 (3 x 3 mm)

#### Maturity status link

ST4E1216, ST4E1240

| Device summary |                  |         |                      |  |  |

|----------------|------------------|---------|----------------------|--|--|

| Part number    | Data rate (Mbps) | Package | Temperature<br>range |  |  |

| ST4E1240DT     | 40               | SO8     | -40°C; 85°C          |  |  |

| ST4E1240IQT    | 40               | DFN8    | -40°C;<br>125°C      |  |  |

| ST4E1216IDT    | 16               | SO8     | -40°C;<br>125°C      |  |  |

#### **Features**

- Meets or exceeds TIA/EIA-485A standard requirements

- 3 V to 5.5 V supply voltage

- Differential output voltage (V<sub>OD</sub>) exceeds 2.1 V at 5 V supply for PROFIBUS compatibility

- High speed: up to 40 Mbps data rate

- More than 64 transceivers on the bus (up to 100 nodes)

- Integrated protections

- Fail-safe receiver (bus open, idle, and shorted)

- Thermal shutdown protection

- Hot-swap capability (with parasitic capacitance up to 100 pF)

- Bus I/O ESD protection

- ±12 kV IEC61000-4-2 contact discharge

- ±30 kV HBM

- ±4 kV IEC61000-4-4 class-A fast transient burst (EFT)

- Low quiescent current in shutdown mode

- Available in industry standard SO-8 and DFN8 for the ST4E1240

### **Applications**

- Factory automation and control

- Motion controllers

- · Building automation and safety

- Video surveillance (building, traffic monitoring)

- Backplane busses

- Grid infrastructure

- Data acquisition (smart meters, seismic networks)

### **Description**

The ST4E1216 and ST4E1240 are low-power differential line transceivers for data transmission standard RS485 applications in half-duplex mode, compatible with either 3.3 V or 5 V rail power supplies, fully operating from 3 V to 5.5 V.

The ST4E1216 and the ST4E1240 operate respectively up to 16 Mbps and 40 Mbps. They are ideal for multipoint applications over extended cable runs. They are robust to ESD transients. In particular, the bus pins support  $\pm 12$  kV IEC 61000-4-2 contact discharge. They also feature robust hot-swap capability during switching on and off, or during hot insertion.

The ST4E1216 is available in SO8 and up to 125 °C. The ST4E1240 is available in SO8 and DFN8 with two temperature ranges as stated in the device summary table.

# 1 Pin configuration

Figure 1. Pin connections

**Table 1. Pin description**

| Name | Pin | I/O            | Description                                                                |

|------|-----|----------------|----------------------------------------------------------------------------|

| R    | 1   | Digital output | Receiver data output                                                       |

| RE   | 2   | Digital input  | Receiver enable input, active low                                          |

| DE   | 3   | Digital input  | Driver enable input, active high                                           |

| D    | 4   | Digital input  | Transmission data input                                                    |

| GND  | 5   | Ground         |                                                                            |

| Α    | 6   | Bus I/O        | Digital bus I/O, A                                                         |

| В    | 7   | Bus I/O        | Digital bus I/O, B                                                         |

| VCC  | 8   | Device supply  | 3 V to 5.5 V supply voltage                                                |

| EP   |     | Exposed pad    | DFN8 only. Connect the exposed pad to ground for optimum thermal behavior. |

DS14542 - Rev 3 page 2/35

# 2 Absolute maximum ratings and operating conditions

Table 2. Absolute maximum ratings

| Symbol           | Parameter                                                                        | Min.                         | Max. | Unit |

|------------------|----------------------------------------------------------------------------------|------------------------------|------|------|

| V <sub>CC</sub>  | Device supply voltage                                                            | -0.5                         | 7    | V    |

|                  | Voltage range at A or B inputs                                                   | -9                           | 14   | V    |

|                  | Input voltage range at any logic pin (referred to an operating $V_{\text{CC}}$ ) | ) -0.3 V <sub>CC</sub> + 0.3 |      |      |

|                  | Short-circuit duration (R, A, B) to GND                                          | Continuous                   |      |      |

| T <sub>stg</sub> | Storage temperature                                                              | -65                          | 150  | °C   |

Note: All voltage values, except the differential voltage, are with respect to network ground terminal.

Table 3. ESD ratings

| Symbol | Parameter                                                                        | Value                              | Unit |

|--------|----------------------------------------------------------------------------------|------------------------------------|------|

|        | IEC61000-4-2 ESD (contact discharge), bus terminals A, B                         | ± 12                               | kV   |

|        | IEC61000-4-4 EFT (fast transient or burst) bus terminals A, B                    | ± 4 (class A)                      | kV   |

| 505    | HBM compliance, bus terminals (A, B) and GND                                     | ± 30 <sup>(1)</sup> <sup>(2)</sup> | kV   |

| ESD    | JEDEC standard 22, test method A114, HBM (Human Body Model), all other terminals | ± 2                                | kV   |

|        | JEDEC standard 22, test method C101, CDM (Charged Device Model), all pins        | ± 1                                | kV   |

- 1. JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- 2. JEDEC standard 22, test method A114, HBM (Human Boby Model), bus terminals (A, B), ≥ ±8 kV (limited by industrial tester capability).

Measurement for 20 A peak, 100 ns Transmission-Line Pulse (TLP), package level at room temperature.

DS14542 - Rev 3 page 3/35

### 3 Electrical characteristics

**Table 4. Operating conditions**

| Symbol          | Parameter                                                  | Min. | Тур. | Max. | Unit   |

|-----------------|------------------------------------------------------------|------|------|------|--------|

| V <sub>CC</sub> | Device supply voltage                                      | 3    |      | 5.5  | V      |

| VI              | Input level at any bus terminal (separated or common-mode) | -7   |      | 12   | V      |

| V <sub>ID</sub> | Differential input voltage                                 | -7   |      | 12   | V      |

| l <sub>a</sub>  | Output current/driver                                      | -70  |      | 70   | mA     |

| I <sub>O</sub>  | Output current/receiver                                    | -70  |      | 70   | IIIA   |

| R <sub>L</sub>  | Differential load resistance                               | 54   | 60   |      | Ω      |

| C <sub>L</sub>  | Differential load capacitance                              |      | 50   |      | pF     |

| D <sub>R</sub>  | Signaling rate for ST4E1216                                |      |      | 16   | Mbps   |

| DR              | Signaling rate for ST4E1240                                |      |      | 40   | IVIDPS |

|                 | Operating free-air temperature for ST4E1216                | -40  |      | 125  |        |

| T <sub>A</sub>  | Operating free-air temperature for ST4E1240 in SO8 package | -40  |      | 85   | °C     |

|                 | Operating free-air temperature for ST4E1240 in DFN8        | -40  |      | 125  |        |

Operation is specified for internal (junction temperature) up to 150 °C. Self-heating due to internal power dissipation should be considered for each application. Maximum junction temperature is internally limited by the thermal shutdown circuit, which disables the driver outputs when the junction temperature reaches 165 °C.

**Table 5. Thermal information**

| Symbol             | Parameter                                     | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------|------|------|------|------|

| D., .              | Thermal resistance, junction-to-ambient, SO8  |      | 125  |      | °C/W |

| R <sub>th-ja</sub> | Thermal resistance, junction-to-ambient, DFN8 |      | 45   |      | C/VV |

**Table 6. Power dissipation**

| Symbol | Parameter                                                                     | Test conditions                                    | Тур. | Unit |

|--------|-------------------------------------------------------------------------------|----------------------------------------------------|------|------|

|        | ST4E1240 power dissipation, with driver and receiver enabled                  | Unterminated, $R_L = 300 \Omega$ , $C_L = 50 pF$   | 310  | mW   |

| $P_D$  | V <sub>CC</sub> = 5.5 V, T = 85 °C, 50% duty cycle at 40 Mbps signaling rate  | RS485-load: $R_L$ = 54 $\Omega$ , $C_L$ = 50 pF    | 370  | mW   |

| י ט    | ST4E1216 power dissipation, with driver and receiver enabled                  | Unterminated, $R_L$ = 300 $\Omega$ , $C_L$ = 50 pF | 140  | mW   |

|        | V <sub>CC</sub> = 5.5 V, T = 125 °C, 50% duty cycle at 16 Mbps signaling rate | RS485-load: $R_L$ = 54 $\Omega$ , $C_L$ = 50 pF    | 220  | mW   |

DS14542 - Rev 3 page 4/35

Table 7. Receiver: operating conditions ( $V_{CC}$  = +3.0 V to 5.5 V,  $T_A$  = Tmin to Tmax, unless otherwise specified. Typical values are at  $V_{CC}$  = 5 V and T = 25 °C)

| Symbol                              | Parameter                                                                     | Test conditions                                                     | Min.                 | Тур. | Max. | Unit |

|-------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------|------|------|------|

|                                     |                                                                               | Receiver/DC                                                         |                      |      |      |      |

| V <sub>TH+</sub>                    | Positive-going input threshold voltage                                        | -7 V ≤ V <sub>CM</sub> ≤ 12 V                                       |                      | -100 | -10  |      |

| V <sub>TH-</sub>                    | Negative-going input threshold voltage                                        | -7 V ≤ V <sub>CM</sub> ≤ 12 V                                       | -200                 | -130 |      | mV   |

| V <sub>HYS</sub>                    | Receivers differential input voltage hysteresis                               |                                                                     |                      | 30   |      |      |

| V <sub>OH</sub>                     | Receivers high-level output voltage                                           | $\overline{RE}$ = GND, I <sub>OH</sub> = -2 mA,<br>(VA-VB) > 200 mV | V <sub>CC</sub> -0.2 |      |      | V    |

| V <sub>OL</sub>                     | Receivers low-level output voltage                                            | $\overline{RE}$ = GND, I <sub>OL</sub> = 2 mA,<br>(VA-VB) < -200 mV |                      |      | 0.2  | V    |

| I <sub>OZ</sub>                     | Receivers output high-impedance current                                       | $0 \le V_R \le V_{CC}, \overline{RE} = V_{CC}$                      | -1                   |      | 1    | μA   |

| I <sub>OS</sub>                     | Receivers outputs short-circuit current                                       | $0 \le V_R \le V_{CC}$                                              | -90                  |      | 90   | mA   |

| R <sub>in</sub>                     | Receivers input impedance                                                     | -7 V ≤ V <sub>incm</sub> ≤ +12 V                                    | 24 (1)               |      |      | kΩ   |

|                                     | Receivers input current                                                       | V <sub>I</sub> = 12 V                                               |                      | 140  | 250  |      |

| l <sub>i</sub>                      | DE = GND, V <sub>CC</sub> = GND or +5.5 V                                     | V <sub>I</sub> = -7 V                                               | -250                 | -120 |      | μA   |

|                                     |                                                                               | Receiver/switching character                                        | istics               |      |      |      |

| t <sub>r</sub> , t <sub>f</sub>     | Receivers output rise/fall time                                               |                                                                     | 0.5                  | 3    | 7.5  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Receivers propagation delay time                                              | $C_1 = 15 pF$                                                       | 12                   | 20   | 25   | ns   |

| t <sub>SK(P)</sub>                  | Receivers pulse skew, $ t_{PHL} - t_{PLH} $ , $\Delta V_{in} = 1.5 \text{ V}$ | 9 <u>1</u> 10 p.                                                    |                      |      | 2    | ns   |

| t <sub>PLZ</sub>                    | Receivers disable time, from low                                              | $C_L$ = 15 pF with 1 k $\Omega$                                     |                      | 5    | 20   | ns   |

| t <sub>PHZ</sub>                    | Receivers disable time, from high                                             | $C_L$ = 15 pF with 1 k $\Omega$                                     |                      | 5    | 30   | ns   |

| t <sub>PZH</sub>                    | Receivers enable time to output high                                          | Driver enabled $C_L$ = 15 pF with 1 k $\Omega$                      |                      | 8    | 30   | ns   |

| t <sub>PZL</sub>                    | Receivers enable time to output low                                           | Driver enabled $C_L$ = 15 pF with 1 k $\Omega$                      |                      | 5    | 20   | ns   |

| t <sub>PZH(shdn)</sub>              | Receivers enable time from shutdown to output high                            | Driver disabled $C_L$ = 15 pF with 1 k $\Omega$                     |                      | 5    | 30   | ns   |

| t <sub>PZL(shdn)</sub>              | Receivers enable time from shutdown to output low                             | Driver disabled $C_L = 15 \text{ pF}$<br>with 1 k $\Omega$          |                      | 8    | 20   | ns   |

<sup>1.</sup> Guaranteed by design simulation in temperature.

DS14542 - Rev 3 page 5/35

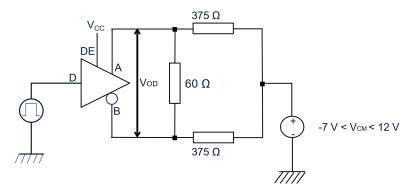

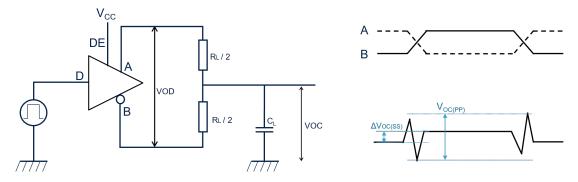

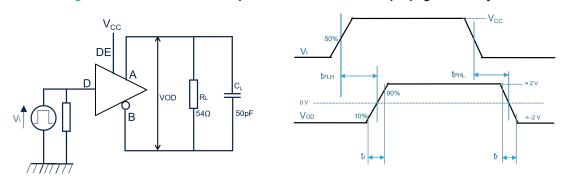

Table 8. Driver: operating conditions ( $V_{CC}$  = +3.0 V to 5.5 V,  $T_A$  = Tmin to Tmax, unless otherwise specified. Typical values are at  $V_{CC}$  = 5 V and T = 25 °C)

| Symbol                              | Parameter                                                 | Test conditions                                                         | Min.                 | Тур.  | Max.  | Unit |

|-------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------|----------------------|-------|-------|------|

|                                     |                                                           | DC driver/DC                                                            |                      |       |       |      |

|                                     |                                                           | R <sub>L</sub> = 60 Ω/375 Ω (Figure 2),<br>V <sub>CC</sub> $\geq$ 4.5 V | 2.1                  |       |       |      |

|                                     | Driver differential output voltage                        | -7 V ≤ V <sub>CM</sub> ≤ +12 V                                          |                      |       |       |      |

| $ V_{OD} $                          | Driver differential output voltage magnitude              | $R_L$ = 60 Ω/375 Ω (Figure 2)                                           | ,_                   |       |       | V    |

|                                     |                                                           | -7 V ≤ V <sub>CM</sub> ≤ +12 V                                          | 1.5                  | 3.5   |       |      |

|                                     |                                                           | R <sub>L</sub> = 54 Ω (Figure 3)                                        | 1.5                  |       |       |      |

| $\Delta  V_{OD} $                   | Change in magnitude of driver differential output voltage | R <sub>L</sub> = 54 Ω, C <sub>L</sub> = 50 pF                           | -50                  |       | +50   | mV   |

| V <sub>OC(SS)</sub>                 | Steady-state common-mode output voltage                   |                                                                         | 1                    | 2.7   | 3 (1) | V    |

| ΔV <sub>OC</sub>                    | Change in differential driver output common-mode voltage  | Center of two 27 Ω load resistors                                       | -0.12                | -0.02 | 0.12  | V    |

| V <sub>OC(PP)</sub>                 | Peak-to-peak driver common-mode output voltage            |                                                                         |                      | 0.9   |       | V    |

| V <sub>OH</sub>                     | Single-ended driver output High                           | A or B output, $I_A$ or $I_B = -20$ mA                                  | V <sub>CC</sub> -0.4 |       |       | V    |

| V <sub>OL</sub>                     | Single-ended driver output Low                            | A or B output, I <sub>A</sub> or I <sub>B</sub> = 20 mA                 |                      |       | 0.95  | V    |

|                                     |                                                           | Driver/switching characteris                                            | tics                 |       |       |      |

| t <sub>r</sub> , t <sub>f</sub>     | Driver differential output rise/fall time                 |                                                                         | 0.5                  | 5     | 7.5   |      |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Driver propagation delay                                  | $R_L = 54 \Omega, C_L = 50 pF$                                          | 4                    | 8     | 20    |      |

| t <sub>SK(P)</sub>                  | Driver pulse skew,  t <sub>PHL</sub> -t <sub>PLH</sub>    |                                                                         |                      |       | 3     | ns   |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Driver disable time                                       |                                                                         |                      | 11    | 20    |      |

| ton ton                             | Driver enable time                                        | Receiver enabled                                                        |                      | 7     | 20    |      |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Driver enable time                                        | Receiver disabled                                                       |                      | 7     | 20    |      |

<sup>1.</sup> For  $V_{CC}$  = 5.5 V and T < 0 °C,  $V_{OC(SS)}$  max = 3.15 V.

Table 9. Input logic interface (D, DE,  $\overline{RE}$ ): ( $V_{CC}$  = +3.0 V to 5.5 V,  $T_A$  = Tmin to Tmax, unless otherwise specified. Typical values are at  $V_{CC}$  = 5 V and T = 25 °C)

| Symbol          | Parameter                                                         | Test conditions                                                                                | Min. | Тур. | Max.            | Unit |

|-----------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-----------------|------|

| $V_{IH}$        | High-level input voltage                                          |                                                                                                | 2    |      | V <sub>CC</sub> | V    |

| V <sub>IL</sub> | Low-level input voltage                                           |                                                                                                | 0    |      | 0.8             | V    |

| I <sub>In</sub> | Input current                                                     | $3 \text{ V} \le \text{V}_{CC} \le 5.5 \text{ V}, \text{V}_{in} = 0 \text{ or } \text{V}_{CC}$ | -5   |      | 5               | μA   |

|                 | Input impedance on first transition (DE, $\overline{\text{RE}}$ ) |                                                                                                |      | 6    |                 | kΩ   |

DS14542 - Rev 3 page 6/35

Table 10. Supply current and protections: ( $V_{CC}$ = +3.0 V to 5.5 V,  $T_A$  = Tmin to Tmax, unless otherwise specified. Typical values are at  $V_{CC}$  = 5 V and T = 25 °C)

| Symbol               | Parameter                                  | Test conditions                                                                       | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------------|---------------------------------------------------------------------------------------|------|------|------|------|

|                      |                                            | Supply current                                                                        |      |      |      |      |

|                      |                                            | Driver and receiver enabled DE = $V_{CC}$ , $\overline{RE}$ = GND, no load            |      | 1.77 | 2.5  | mA   |

|                      | I <sub>CC</sub> Supply current (quiescent) | Driver enabled, receiver disabled DE = $V_{CC}$ , $\overline{RE} = V_{CC}$ , no load  |      | 1    | 1.8  | mA   |

| ICC                  |                                            | Driver disabled, receiver enabled DE = GND, RE = GND, no load                         |      | 1    | 1.8  | mA   |

|                      |                                            | Driver and receiver disabled (shutdown mode) DE = GND, RE = V <sub>CC</sub> , no load |      | 0.6  | 3.5  | μА   |

| T <sub>TSD</sub>     | Thermal shutdown threshold                 |                                                                                       |      | 165  |      | °C   |

| T <sub>TSD_HYS</sub> | Thermal shutdown hysteresis                |                                                                                       |      | 13   |      |      |

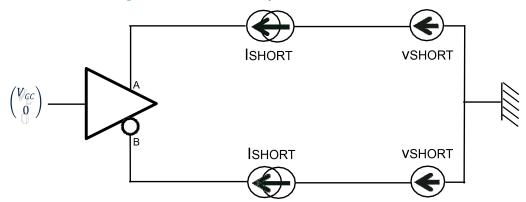

| I <sub>OS</sub>      | Driver short-circuit output current        | -7 V < V <sub>SHORT</sub> < +12 V                                                     | -250 |      | 250  | mA   |

DS14542 - Rev 3 page 7/35

# 4 Test circuits

In the schematics below,  $\mathbf{C}_{\mathbf{L}}$  includes fixture and instrumentation capacitance.

Figure 2. Driver differential output voltage with common-mode load

Figure 3. Driver differential and common-mode output with RS-485 load

Figure 4. Driver differential output rise and fall times and propagation delays

DS14542 - Rev 3 page 8/35

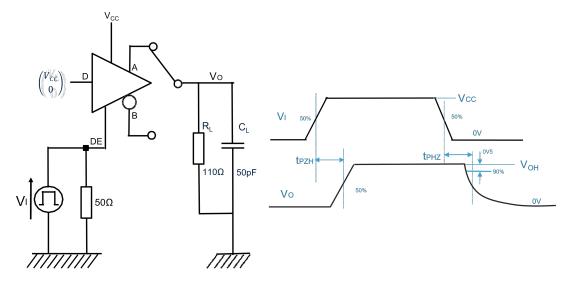

Figure 5. Driver enable and disable times with active high output and pull-down load

Figure 6. Driver enable and disable times with active low output and pull-up load

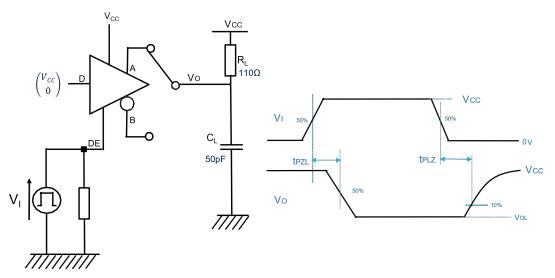

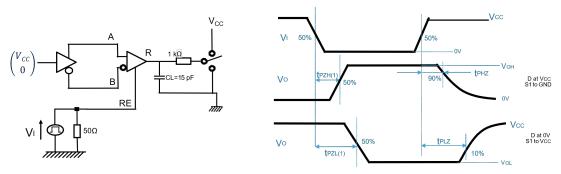

Figure 7. Receiver output rise and fall times and propagation delay

DS14542 - Rev 3 page 9/35

Figure 8. Receiver enable/disable times with driver enabled

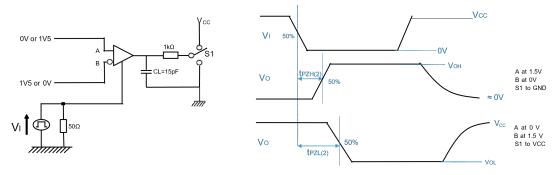

Figure 9. Receiver enable/disable times with driver disabled

Figure 10. Short-circuit output current measurement

When one of the driver outputs is shorted to a voltage source (named  $V_{SHORT}$ ) between -7 V to +12 V stabilized, the current does not exceed 250 mA and the driver is protected.

DS14542 - Rev 3 page 10/35

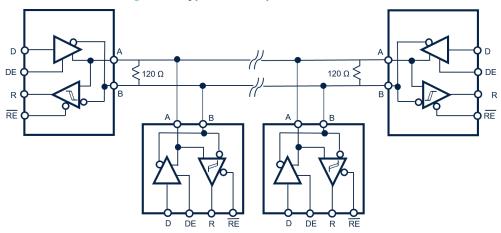

Figure 11. Typical half-duplex RS485 network

DS14542 - Rev 3 page 11/35

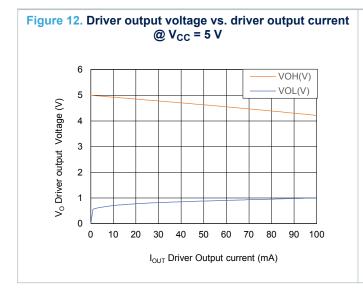

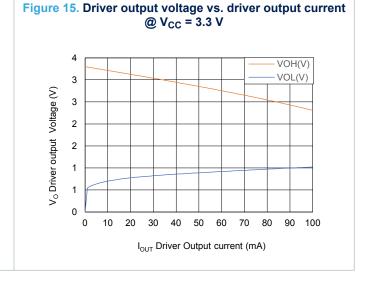

# Typical characteristics - All devices

Figure 13. Driver differential output voltage vs. driver output current @ V<sub>CC</sub> = 5 V

DS14542 - Rev 3 page 12/35

0 10 20

Figure 16. Driver differential output voltage vs. driver output current @ V<sub>CC</sub> = 3.3 V 4 Driver Differential output Voltage (V) 3 3 2 2 1

40 50 60 70 80

$I_{OUT}$  Driver Output current (mA)

90 100

Figure 17. Receiver output vs. input @ V<sub>CC</sub> = 3 V 3.5 Vth (0V) Vth (12V) Vth (-7V) 3 2.5 Receiver output (V) 2 1.5 0.5 -170 -160 -150 -140 -130 -120 -110 -100 -90 -80 -70 -60 VID Differential input voltage (mV)

Figure 18. Driver output current vs. power supply with  $R_L=54\Omega$ 80 70 60 Driver output current (mA) 50 40 30 20 10 2.50 3.00 3.50 4.00 4.50 5.00 5.50 6.00 V<sub>CC</sub> suply voltage (V)

DS14542 - Rev 3 page 13/35

### 5.1 Typical characteristics - ST4E1240 - SO8 package

DS14542 - Rev 3 page 14/35

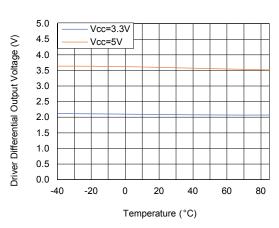

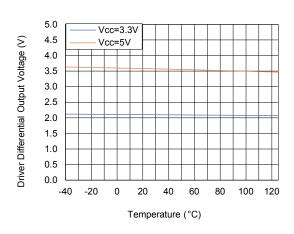

Figure 24. Differential driver output voltage vs. temperature

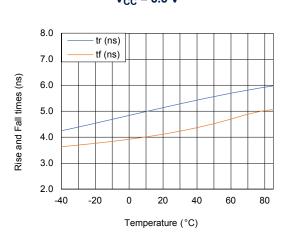

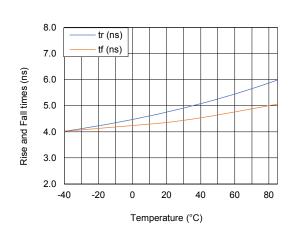

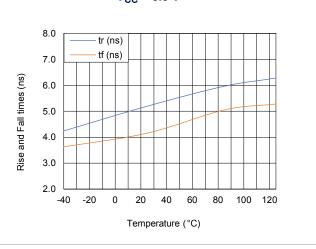

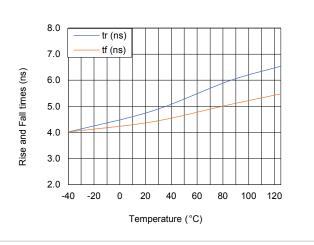

Figure 25. Driver rise and fall times vs. temperature @  $V_{CC}$  = 5.5 V

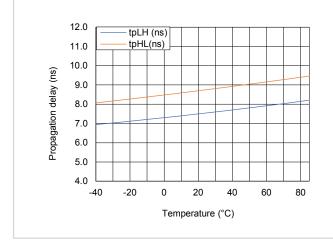

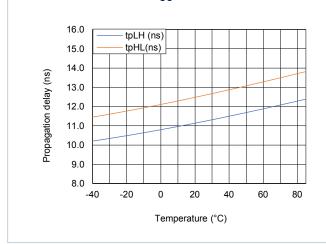

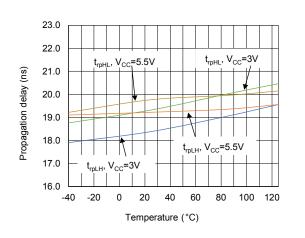

Figure 26. Driver propagation delay vs. temperature @  $V_{CC}$  = 5.5 V

Figure 27. Driver rise and fall times vs. temperature @  $V_{CC}$  = 3 V

Figure 28. Driver propagation delay vs. temperature @  $V_{CC} = 3 V$

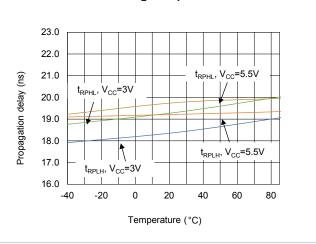

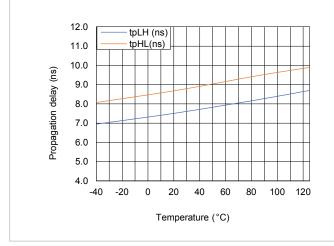

Figure 29. Receiver propagation delay vs. temperature, with C<sub>L</sub> = 20 pF

DS14542 - Rev 3 page 15/35

DS14542 - Rev 3 page 16/35

### 5.2 Typical characteristics - ST4E1216 and ST4E1240 - DFN8 package

GND,  $\overline{RE}$  = GND, @  $V_{CC}$  = 3.3 V and  $V_{CC}$  = 5 V 2.0 Vcc=3.3V Vcc=5V 1.6 Icc\_Rx\_ON\_Tx\_OFF (mA) 1.2 0.8 0.4 -40 -20 0 20 40 60 80 100 120 Temperature (°C)

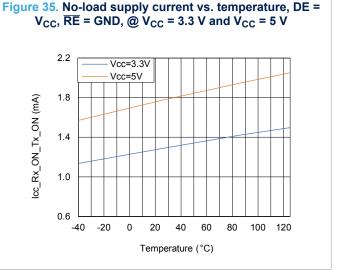

Figure 33. No-load supply current vs. temperature, DE =

$V_{CC}$ ,  $\overline{RE} = V_{CC}$ , @  $V_{CC} = 3.3$  and  $V_{CC} = 5$  V 2.0 Vcc=3.3V Vcc=5V 1.6 Icc\_Rx\_OFF\_Tx\_ON (mA) 1.2 0.8 0.4 -40 -20 0 20 40 60 80 100 120 Temperature (°C)

Figure 34. No-load supply current vs. temperature, DE =

DS14542 - Rev 3 page 17/35

Figure 36. Differential driver output voltage vs. temperature

Figure 37. Driver rise and fall times vs. temperature @  $V_{CC}$  = 5.5 V

Figure 38. Driver propagation delay vs. temperature @  $V_{CC}$  = 5.5 V

Figure 39. Driver rise and fall times vs. temperature @  $V_{CC}$  = 3 V

Figure 40. Driver propagation delay vs. temperature @  $V_{CC} = 3 V$

Figure 41. Receiver propagation delay vs. temperature, with C<sub>L</sub> = 20 pF

DS14542 - Rev 3 page 18/35

DS14542 - Rev 3 page 19/35

### 6 Detailed description

The ST4E1216 and ST4E1240 are a half-duplex differential RS-485 transceiver, suitable for data transmission up to 40 Mbps. The devices support 64 bus nodes minimum. The receiver and driver are activated through the dedicated pins DE and RE. Its functional block diagram is shown below.

VCC DE RE GND

Figure 44. Block diagram

#### **Device functional modes**

The various functional modes of the ST4E1216 and ST4E1240 are detailed in the following function tables.

When the driver enable pin DE is high, the driver is enabled. The differential signal  $V_{OD} = V_A - V_B$  follows the logic state of the signal present on input D, that is  $V_{OD}$  is positive if D is high,  $V_{OD}$  is negative when D is low.

When DE logic is low, A and B are set to high impedance, the driver is disabled, and the D signal does not impact the outputs. The DE pin has an internal pull-down resistor to the ground, which disables the driver by default if left open.

The D pin has an internal pull-up resistor to  $V_{CC}$ , thus when left open while the driver is enabled, output A is high and B low by default.

| INPUT D | ENABLE DE | OUTPUT A | OUTPUT B | Function                           |

|---------|-----------|----------|----------|------------------------------------|

| Н       | Н         | Н        | L        | Actively drive bus high            |

| L       | Н         | L        | Н        | Actively drive bus low             |

| X       | L         | Z        | Z        | Driver disabled                    |

| X       | Open      | Z        | Z        | Driver disabled by default         |

| Open    | Н         | Н        | L        | Actively drive bus high by default |

Table 11. Driver truth table

When the receiver enable pin  $\overline{RE}$  is logic low, the receiver is enabled. When the differential input voltage  $V_{ID} = V_A - V_B$  is higher than the positive input threshold  $V_{TH+}$ , the receiver output R turns high. When  $V_{ID}$  is below the negative threshold  $V_{TH-}$ , the output R turns low. And when  $V_{ID}$  is in-between both threshold voltages, R is indeterminate.

If  $\overline{RE}$  is logic high, R is high impedance and the  $V_{ID}$  polarity and voltage do not impact it. The  $\overline{RE}$  pin has an internal pull-up resistor, thus when left open, the receiver output is disabled by default.

The ST4E1216 and ST4E1240 architecture turns receiver output in a fail-safe high state when the transceiver is disconnected from the bus (open), the bus lines A, B are shorted together (short), or the bus is not actively driven (idle).

DS14542 - Rev 3 page 20/35

Table 12. Receiver truth table

| Differential input V <sub>ID</sub> = V <sub>A</sub> -V <sub>B</sub> | ENABLE RE | OUTPUT R | Function                     |

|---------------------------------------------------------------------|-----------|----------|------------------------------|

| V <sub>TH+</sub> < V <sub>ID</sub>                                  | L         | Н        | Receive valid bus high       |

| $V_{TH-} < V_{ID} < V_{TH+}$                                        | L         | I        | Indeterminate bus state      |

| V <sub>ID</sub> < V <sub>TH-</sub>                                  | L         | L        | Receive valid bus low        |

| X                                                                   | Н         | Z        | Receiver disabled            |

| X                                                                   | Open      | Z        | Receiver disabled by default |

| Open-circuit bus                                                    | L         | Н        | Fail-safe high output        |

| Short-circuit bus                                                   | L         | Н        | Fail-safe high output        |

| Idle (terminated) bus                                               | L         | Н        | Fail-safe high output        |

#### Shutdown mode

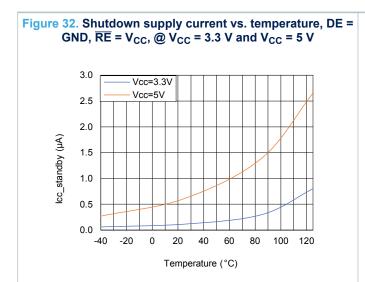

Shutdown mode is initiated when driving DE low and  $\overline{RE}$  high. In this state, the device draws less than 3.5  $\mu A$  of current in all temperature and power supply conditions. Shutdown mode is entered in typically 2  $\mu s$  at  $V_{CC}$  5 V and ambient temperature of 25  $^{\circ}C$ .

The ST4E1216 and ST4E1240 are designed for bidirectional data communications on multipoint bus transmission lines. Figure 11 shows a typical network application circuit. To minimize reflections, the line should be terminated at both ends with its characteristic impedance and stub lengths to be kept as short as possible from the main line.

#### Fail-safe receiver

The ST4E1216 and ST4E1240 have a fail-safe receiver to ensure a logic level on the bus and prevent any indeterminate state. The following conditions can be detected.

- Open bus such as a disconnected connector

- A shorted bus such as a damaged cable creating a short of the twisted pair

- An idle bus that occurs when no device on the bus is actively driving

In any of these cases, the differential receiver drives a fail-safe logic high level so that the output of the receiver is not indeterminate.

#### **Hot-swap capability**

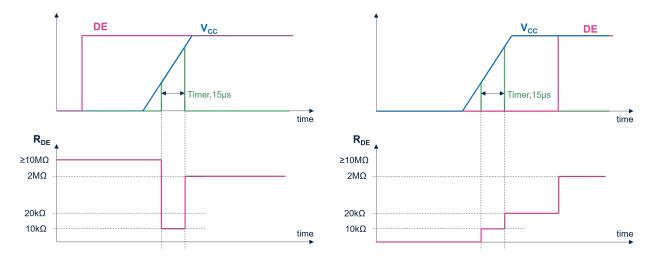

The enable pins DE and  $\overline{\text{RE}}$  are critical pins during a switch-on or plug-in phase on the RS485 bus. To prevent these pins from driving into unwanted states on the bus due to possible disturbances during these steps, the ST4E1216 and ST4E1240 features an integrated hot-swap structure to avoid these potential problems.

Assuming a parasitic capacitance may be present on the board between the nodes DE and GND, or  $\overline{RE}$  and  $V_{CC}$ ; when the power supply rises, the MCU may drive an undetermined state on the nodes DE and  $\overline{RE}$ . Depending on the input impedance on nodes DE and  $\overline{RE}$ , it can generate an unwanted signal on bus pins A, B.

A parasitic capacitance up to 100 pF is efficiently discharged with the hot-swap structure of the ST4E1216 and ST4E1240.

The new ST RS485 transceivers manage dynamically the input impedance on DE and  $\overline{RE}$  versus  $V_{CC}$ . A typical transient resistor of 6 k $\Omega$  is seen during the rising edge of the power supply, during a defined time of 15  $\mu$ s typically. This allows fast discharge of parasitic capacitance, preventing any unwanted signal on the bus pins. A second typical transient resistor of 20 k $\Omega$  is still present until the  $V_{CC}$  supply is fully established. Then, the 2 M $\Omega$  resistors are the connected pull-up or pull-down resistor on both DE and  $\overline{RE}$  terminals during normal ON operation for current consumption considerations. An example is shown below for the impedance management on the DE terminal. Such a structure is also present on  $\overline{RE}$  versus  $V_{CC}$ .

DS14542 - Rev 3 page 21/35

Figure 45. Hot-swap management with DE rising high before and after V<sub>CC</sub>

#### Electrostatic discharge (ESD) protection

The ST4E1216 and ST4E1240 have internal protection against electrostatic discharge (ESD).

At circuit level, the ST4E1216 and ST4E1240 comply with the human body model (ANSI/ESDA/JEDEC JS-001) to guarantee robustness during the manufacturing process. All the pins of the ST4E1216 and ST4E1240 sustain 2 kV.

Because these transceivers are part of a system and can be connected to its outside through the bus terminals A and B, an ESD protection is implemented on A and B to comply with IEC 61000-4-2 standard.

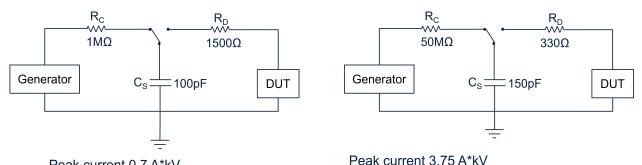

The schematic below compares the simplified pulse generator between the circuit-level ESD pulse and the system-level ESD pulse.

Figure 46. HBM JEDEC (left) and IEC61000-4-2 (right) generator simplified schematics

Peak current 0.7 A\*kV Rise time of pulse: 2 ns to 10 ns

Rise time of pulse: 0.6 ns to 1 ns

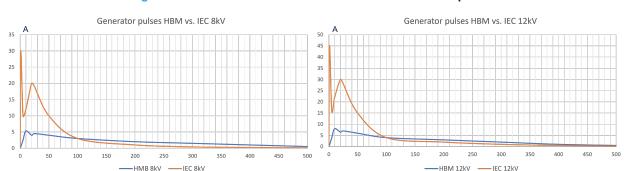

For an equivalent ESD pulse voltage, the peak current and rise time of the pulse is much higher for the IEC61000-4-2 than for the HBM. This can be shown by the pulse's diagrams below, for 8 kV and 12 kV respectively.

DS14542 - Rev 3 page 22/35

Figure 47. HBM JEDEC and IEC61000-4-2 waveforms comparison

The IEC61000-4-2 standard is more severe than the HBM ESD test and significantly increases the robustness of the equipment. IEC61000-4-2 8 kV protections are commonly implemented.

The ST4E1216 and ST4E1240 furthermore increase the robustness of systems thanks to the dedicated IEC61000-4-2 12 kV protections on bus terminals A and B. There are two methods of ESD testing: contact discharge and air discharge. In the contact discharge method, the electrode of the test generator is held in contact with an exposed conductor on the equipment under test (EUT). In the air discharge, the electrode of the generator is moved from a distance towards the EUT until an arc occurs. The contact discharge offers the best reproducibility and is chosen to be the test method for IEC61000-4-2.

The ST4E1216 and ST4E1240 comply with IEC61000-4-2 12 kV contact discharge.

DS14542 - Rev 3 page 23/35

# 7 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

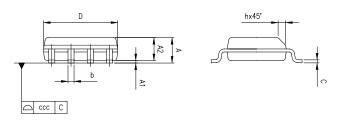

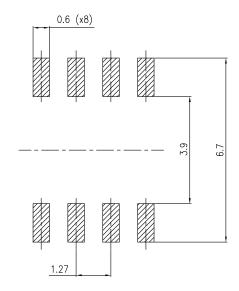

### 7.1 SO8 package information

Figure 48. SO8 package outline

Table 13. SO8 package mechanical data

|      | Dimensions |             |      |       |        |       |  |

|------|------------|-------------|------|-------|--------|-------|--|

| Ref. |            | Millimeters |      |       | Inches |       |  |

|      | Min.       | Тур.        | Max. | Min.  | Тур.   | Max.  |  |

| Α    |            |             | 1.75 |       |        | 0.069 |  |

| A1   | 0.10       |             | 0.25 | 0.04  |        | 0.010 |  |

| A2   | 1.25       |             |      | 0.049 |        |       |  |

| b    | 0.28       | 0.40        | 0.48 | 0.011 | 0.016  | 0.019 |  |

| С    | 0.17       |             | 0.23 | 0.007 |        | 0.010 |  |

| D    | 4.80       | 4.90        | 5.00 | 0.189 | 0.193  | 0.197 |  |

| E    | 5.80       | 6.00        | 6.20 | 0.228 | 0.236  | 0.244 |  |

| E1   | 3.80       | 3.90        | 4.00 | 0.150 | 0.154  | 0.157 |  |

| е    |            | 1.27        |      |       | 0.050  |       |  |

| h    | 0.25       |             | 0.50 | 0.010 |        | 0.020 |  |

| L    | 0.40       | 0.635       | 1.27 | 0.016 |        | 0.050 |  |

| L1   |            | 1.04        |      |       | 0.040  |       |  |

| k    | 1°         |             | 8°   | 1°    |        | 8°    |  |

| CCC  |            |             | 0.10 |       |        | 0.004 |  |

DS14542 - Rev 3 page 24/35

Figure 49. SO8 recommended footprint (mm)

DS14542 - Rev 3 page 25/35

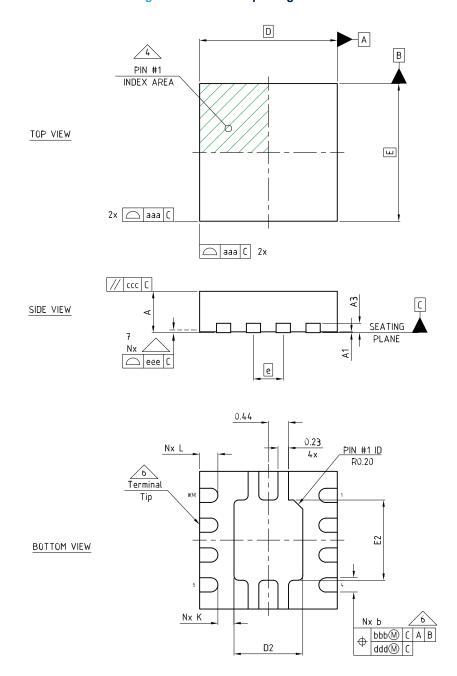

### 7.2 DFN8 3x3 package information

Figure 50. DFN8 3x3 package outline

DS14542 - Rev 3 page 26/35

Table 14. DFN8 3x3 mechanical data

| Ref. | Dimensions (mm) |           |      |  |

|------|-----------------|-----------|------|--|

|      | Min.            | Тур.      | Max. |  |

| А    | 0.80            | 0.90      | 1.00 |  |

| A1   | 0.00            | 0.02      | 0.05 |  |

| A3   |                 | 0.203 REF |      |  |

| b    | 0.26            | 0.31      | 0.36 |  |

| D    |                 | 3 BSC     |      |  |

| Е    | 3 BSC           |           |      |  |

| е    | 0.65 BSC        |           |      |  |

| D2   | 1.45            | 1.50      | 1.55 |  |

| E2   | 1.70            | 1.75      | 1.80 |  |

| K    | 0.20            | -         | -    |  |

| L    | 0.30            | 0.40      | 0.50 |  |

| N    | 8               |           |      |  |

| Ne   | 4               |           |      |  |

|      | TOLERANCE       |           |      |  |

| aaa  |                 | 0.05      |      |  |

| bbb  | 0.10            |           |      |  |

| ccc  |                 | 0.10      |      |  |

| ddd  |                 | 0.05      |      |  |

| eee  |                 | 0.08      |      |  |

DS14542 - Rev 3 page 27/35

1.6

Figure 51. DFN8 3x3 recommended footprint

DS14542 - Rev 3 page 28/35

# 8 Ordering information

Table 15. Order code

| Order code  | Temperature range | Package | Marking  |

|-------------|-------------------|---------|----------|

| ST4E1216IDT | -40 °C to +125 °C | SO-8    | T4E1216I |

| ST4E1240DT  | -40 °C to +85 °C  | 30-0    | T4E1240  |

| ST4E1240IQT | -40 °C to +125 °C | DFN8    | 2401     |

DS14542 - Rev 3 page 29/35

## **Revision history**

**Table 16. Document revision history**

| Date        | Revision | Changes                                                                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 09-Jan-2024 | 1        | Initial release.                                                                                                                              |

| 12-Feb-2024 | 2        | Added new part number ST4E1216.  Updated features and description on the cover page, Figure 1 and Table 14. Order code.                       |

| 06-Nov-2024 | 3        | Added new package DFN8 3 x 3 and Section 7.2.  Updated figure, features and device summary on the cover page, Figure 1, Table 3 and Table 15. |

DS14542 - Rev 3 page 30/35

## **Contents**

| 1  | Pin                        | configuration                                                  | 2  |  |  |

|----|----------------------------|----------------------------------------------------------------|----|--|--|

| 2  | Abs                        | Absolute maximum ratings and operating conditions              |    |  |  |

| 3  | Electrical characteristics |                                                                |    |  |  |

| 4  | Test circuits              |                                                                |    |  |  |

| 5  | Турі                       | ical characteristics - All devices                             | 12 |  |  |

|    | 5.1                        | Typical characteristics - ST4E1240 - SO8 package               | 14 |  |  |

|    | 5.2                        | Typical characteristics - ST4E1216 and ST4E1240 - DFN8 package | 17 |  |  |

| 6  | Deta                       | ailed description                                              | 20 |  |  |

| 7  | Pac                        | kage information                                               |    |  |  |

|    | 7.1                        | SO8 package information                                        | 24 |  |  |

|    | 7.2                        | DFN8 3x3 package information                                   | 26 |  |  |

| 8  | Ord                        | ering information                                              | 29 |  |  |

| Re | vision                     | history                                                        |    |  |  |

DS14542 - Rev 3 page 31/35

## **List of tables**

| Table 1.  | Pin description                                                                                                                                                                                                   | 2  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.  | Absolute maximum ratings                                                                                                                                                                                          | 3  |

| Table 3.  | ESD ratings                                                                                                                                                                                                       | 3  |

| Table 4.  | Operating conditions                                                                                                                                                                                              | 4  |

| Table 5.  | Thermal information                                                                                                                                                                                               | 4  |

| Table 6.  | Power dissipation                                                                                                                                                                                                 | 4  |

| Table 7.  | Receiver: operating conditions ( $V_{CC}$ = +3.0 V to 5.5 V, $T_A$ = Tmin to Tmax, unless otherwise specified. Typical values are at $V_{CC}$ = 5 V and T = 25 °C)                                                | 5  |

| Table 8.  | Driver: operating conditions ( $V_{CC}$ = +3.0 V to 5.5 V, $T_A$ = Tmin to Tmax, unless otherwise specified. Typical values are at $V_{CC}$ = 5 V and T = 25 °C)                                                  |    |

| Table 9.  | Input logic interface (D, DE, $\overline{\text{RE}}$ ): (V <sub>CC</sub> = +3.0 V to 5.5 V, T <sub>A</sub> = Tmin to Tmax, unless otherwise specified. Typical values are at V <sub>CC</sub> = 5 V and T = 25 °C) | 6  |

| Table 10. | Supply current and protections: ( $V_{CC}$ = +3.0 V to 5.5 V, $T_A$ = Tmin to Tmax, unless otherwise specified. Typical values are at $V_{CC}$ = 5 V and T = 25 °C)                                               | 7  |

| Table 11. | Driver truth table                                                                                                                                                                                                | 20 |

| Table 12. | Receiver truth table                                                                                                                                                                                              | 21 |

| Table 13. | SO8 package mechanical data                                                                                                                                                                                       | 24 |

| Table 14. | DFN8 3x3 mechanical data                                                                                                                                                                                          |    |

| Table 15. | Order code                                                                                                                                                                                                        | 29 |

| Table 16. | Document revision history                                                                                                                                                                                         | 30 |

|           |                                                                                                                                                                                                                   |    |

DS14542 - Rev 3 page 32/35

# **List of figures**

| Figure 1.                | Pin connections                                                                                                                            |    |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.                | Driver differential output voltage with common-mode load                                                                                   | 8  |

| Figure 3.                | Driver differential and common-mode output with RS-485 load                                                                                |    |

| Figure 4.                | Driver differential output rise and fall times and propagation delays                                                                      |    |

| Figure 5.                | Driver enable and disable times with active high output and pull-down load                                                                 |    |

| Figure 6.                | Driver enable and disable times with active low output and pull-up load                                                                    |    |

| Figure 7.                | Receiver output rise and fall times and propagation delay                                                                                  |    |

| Figure 8.                | Receiver enable/disable times with driver enabled.                                                                                         |    |

| Figure 9.                | Receiver enable/disable times with driver disabled                                                                                         |    |

| Figure 10. Figure 11.    | Typical half-duplex RS485 network                                                                                                          |    |

| Figure 12.               | Driver output voltage vs. driver output current @ V <sub>CC</sub> = 5 V                                                                    |    |

| Figure 13.               | Driver differential output voltage vs. driver output current @ $V_{CC} = 5 \text{ V}$                                                      |    |

| _                        |                                                                                                                                            |    |

| Figure 14.               | Receiver output vs. input @ V <sub>CC</sub> = 5.5 V                                                                                        |    |

| Figure 15.               | Driver output voltage vs. driver output current @ V <sub>CC</sub> = 3.3 V                                                                  |    |

| Figure 16.               | Driver differential output voltage vs. driver output current @ V <sub>CC</sub> = 3.3 V                                                     |    |

| Figure 17.               | Receiver output vs. input @ V <sub>CC</sub> = 3 V                                                                                          |    |

| Figure 18.               | Driver output current vs. power supply with R <sub>L</sub> =54 $\Omega$                                                                    |    |

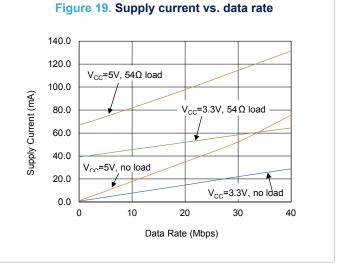

| Figure 19.               | Supply current vs. data rate                                                                                                               |    |

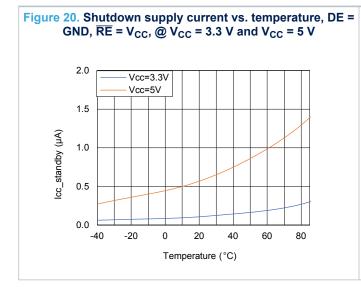

| Figure 20.               | Shutdown supply current vs. temperature, DE = GND, $\overline{RE}$ = V <sub>CC</sub> , @ V <sub>CC</sub> = 3.3 V and V <sub>CC</sub> = 5 V |    |

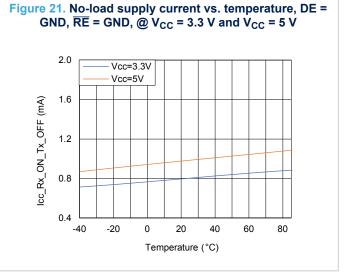

| Figure 21.               | No-load supply current vs. temperature, DE = GND, $\overline{RE}$ = GND, @ $V_{CC}$ = 3.3 V and $V_{CC}$ = 5 V                             |    |

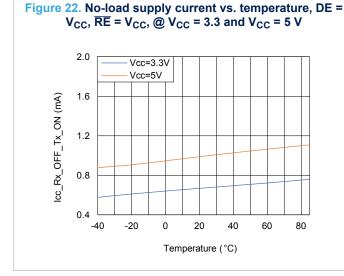

| Figure 22.               | No-load supply current vs. temperature, DE = $V_{CC}$ , $\overline{RE}$ = $V_{CC}$ , @ $V_{CC}$ = 3.3 and $V_{CC}$ = 5 V                   |    |

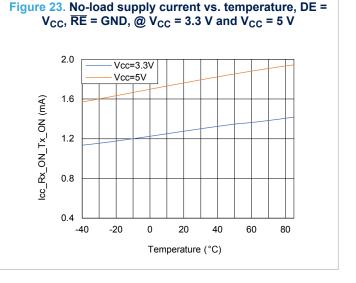

| Figure 23.               | No-load supply current vs. temperature, DE = $V_{CC}$ , $\overline{RE}$ = GND, @ $V_{CC}$ = 3.3 V and $V_{CC}$ = 5 V                       | 14 |

| Figure 24.               | Differential driver output voltage vs. temperature                                                                                         |    |

| Figure 25.               | Driver rise and fall times vs. temperature @ V <sub>CC</sub> = 5.5 V                                                                       |    |

| Figure 26.               | Driver propagation delay vs. temperature @ V <sub>CC</sub> = 5.5 V                                                                         | 15 |

| Figure 27.               | Driver rise and fall times vs. temperature @ V <sub>CC</sub> = 3 V                                                                         | 15 |

| Figure 28.               | Driver propagation delay vs. temperature @ V <sub>CC</sub> = 3 V                                                                           | 15 |

| Figure 29.               | Receiver propagation delay vs. temperature, with C <sub>L</sub> = 20 pF                                                                    | 15 |

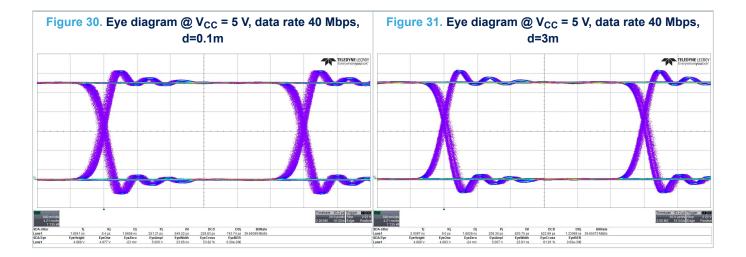

| Figure 30.               | Eye diagram @ V <sub>CC</sub> = 5 V, data rate 40 Mbps, d=0.1m                                                                             | 16 |

| Figure 31.               | Eye diagram @ V <sub>CC</sub> = 5 V, data rate 40 Mbps, d=3m                                                                               | 16 |

| Figure 32.               | Shutdown supply current vs. temperature, DE = GND, $\overline{RE}$ = $V_{CC}$ , @ $V_{CC}$ = 3.3 V and $V_{CC}$ = 5 V                      | 17 |

| Figure 33.               | No-load supply current vs. temperature, DE = GND, $\overline{RE}$ = GND, @ $V_{CC}$ = 3.3 V and $V_{CC}$ = 5 V                             | 17 |

| Figure 34.               | No-load supply current vs. temperature, DE = $V_{CC}$ , $\overline{RE} = V_{CC}$ , @ $V_{CC} = 3.3$ and $V_{CC} = 5 V \dots$               |    |

| Figure 35.               | No-load supply current vs. temperature, DE = $V_{CC}$ , $\overline{RE}$ = GND, @ $V_{CC}$ = 3.3 V and $V_{CC}$ = 5 V                       |    |

| Figure 36.               | Differential driver output voltage vs. temperature                                                                                         |    |

| Figure 37.               | Driver rise and fall times vs. temperature @ V <sub>CC</sub> = 5.5 V                                                                       |    |

| Figure 38.               | Driver propagation delay vs. temperature @ V <sub>CC</sub> = 5.5 V                                                                         |    |

| Figure 39.               | Driver rise and fall times vs. temperature @ V <sub>CC</sub> = 3 V                                                                         |    |

| Figure 40.               | Driver propagation delay vs. temperature @ V <sub>CC</sub> = 3 V                                                                           |    |

| Figure 41.               | Receiver propagation delay vs. temperature, with $C_L = 20 \text{ pF} \dots$                                                               |    |

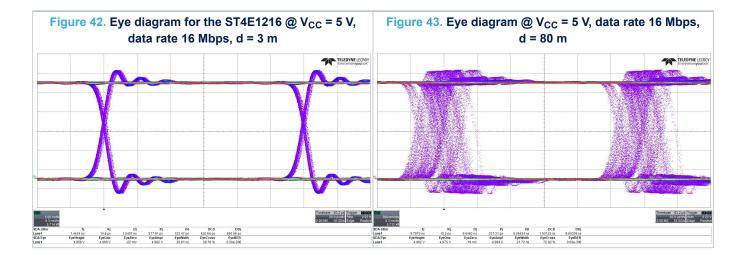

| Figure 42.               | Eye diagram for the ST4E1216 @ $V_{CC}$ = 5 V, data rate 16 Mbps, d = 3 m                                                                  |    |

|                          | Eye diagram @ V <sub>CC</sub> = 5 V, data rate 16 Mbps, d = 80 m                                                                           |    |

| Figure 43.               |                                                                                                                                            |    |

| Figure 44.               | Block diagram                                                                                                                              |    |

| Figure 45.               | Hot-swap management with DE rising high before and after V <sub>CC</sub>                                                                   |    |

| Figure 46.               | HBM JEDEC (left) and IEC61000-4-2 (right) generator simplified schematics                                                                  |    |

| Figure 47.<br>Figure 48. | HBM JEDEC and IEC61000-4-2 waveforms comparison                                                                                            |    |

| Figure 49.               | SO8 recommended footprint (mm)                                                                                                             |    |

| Figure 50.               | DFN8 3x3 package outline                                                                                                                   |    |

| 94.0 00.                 | Di 110 one pustage dumie                                                                                                                   | 20 |

DS14542 - Rev 3 page 33/35

List of figures

| Figure 51. | DFN8 3x3 recommended foot | rint | 28 |

|------------|---------------------------|------|----|

|------------|---------------------------|------|----|

DS14542 - Rev 3 page 34/35

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS14542 - Rev 3 page 35/35